NAND闪存单元排列到页面和块中。 数据写在页面上,但是最小擦除单位是块。 由于闪存的特性,每个编程和擦除(P / E)周期都会使单元磨损,从而使闪存只能在有限的时间内可用。

过去,闪存的预期寿命在很大程度上取决于其类型。 每个单元仅存储1 bit的单层单元(SLC)被认为是最可靠,寿命最长的单元。 多层单元(MLC)(每个单元存储2 bits)的等级接近SLC。 三层和四层单元TLC / QLC仅适用于消费类使用,其低耐久性不能满足企业和工业应用的需求。

得益于技术的巨大进步,闪存的发展已经取得了长足的进步,这主要归功于强大的闪存控制器,可实现更高的可靠性和更长的产品使用寿命。

在本文中,我们讨论了最常见的闪存控制器功能之一,可帮助最大限度地提高闪存的预期寿命。

磨损均衡

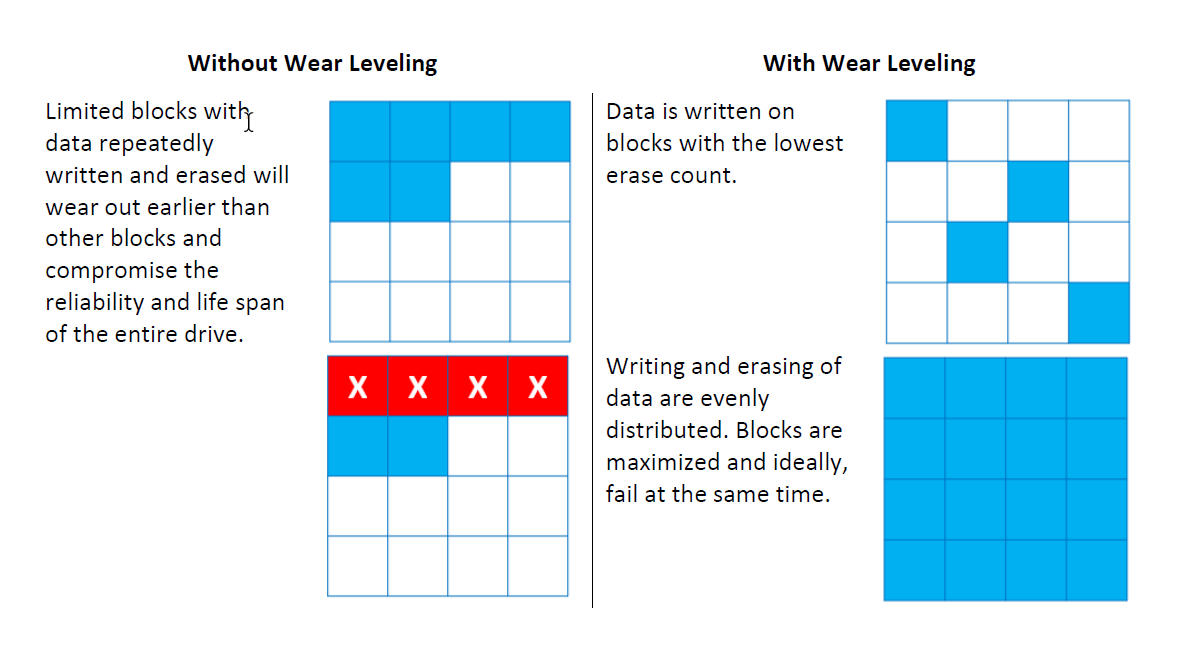

磨损均衡机制允许闪存设备在所有块之间平均分配P / E周期。 它可以防止过度使用的块过早磨损,因此可以最大程度地使用所有块。 磨损均衡可延长使用寿命,并提高存储设备的可靠性和耐用性。

图1. 带和不带磨损均衡的存储设备的图形表示

磨损均衡有三种类型

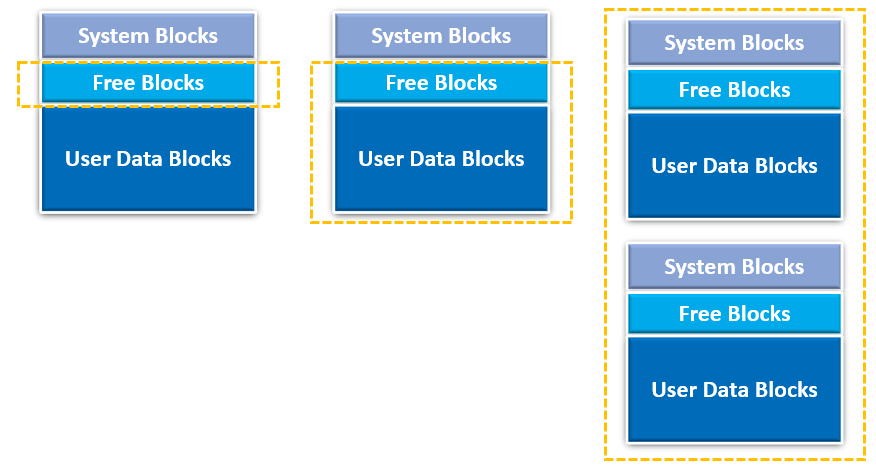

- 动态–确保仅在擦除次数最少的块上写入数据。 不利的一面是,磨损均衡仅限于“热”或频繁修改的区域,因此那些很少访问的静态数据的块不包括在可用空间池中,从而限制了通过磨损均衡的块的数量。

- 静态–包括磨损均衡过程中的静态数据或“冷”块。 如果块包含静态或很少访问的数据,则其写入/擦除计数很低。 数据从“冷”块移至“热”块,并将释放的块添加到可用空间池中,以备将来使用。 重新分配静态数据是一个更复杂的过程,因为它涉及多个操作以移动静态数据。 虽然在延长闪存寿命方面更有效,但静态磨损均衡仅覆盖单个闪存芯片。

- 全局–通过包括可用空间和带有静态数据的块,可以像静态磨损均衡一样工作,但是主要区别在于其覆盖范围扩展到整个闪存设备。

下图说明了执行区域的差异:

|

动态磨损均衡

|

静态磨损均衡

|

全局磨损均衡

|

图2. 动态、静态和全局磨损均衡的执行区域差异。 图片参考:嵌入式计算

ATP增强的磨损均衡

ATP使用先进的算法来实现其闪存产品的全局磨损均衡,该算法执行动态和静态磨损均衡,以确保闪存产品在其使用寿命内得到最大程度的使用。

ATP增强型磨损均衡将一个驱动器中的所有NAND闪存组件作为统一的内存管理单元进行处理和管理。 磨损均衡由闪存控制器执行,并且独立于主机系统,从而将对系统性能的影响降至最低。

这个怎么运作:

“增强的磨损均衡”机制有四个主要步骤:

- 建立并更新链路表,该表用于将主机的逻辑地址转换为闪存的物理地址。

- 记录一个区域中所有块的“擦除计数”,并将它们保存到磨损均衡表中。 该表由控制器中的RAM寄存器单元维护。 该表会将每个块的“擦除计数”保留在闪存IC中。

- 查找静态块(擦除计数为“ 0”)并将该块地址保存在磨损均衡指针中。 该指针用于选择要交换的下一个可用块。

- 从备用池中取出一个块时,请检查“擦除计数”。 如果过计数块大于备用块,则将静态备用块替换为过计数块。 “过多计数”表示该块的擦除计数已经高于磨损计数寄存器,因此应尽快交换该块。

Conclusion

Wear leveling is needed to address the finite program/erase capability of NAND flash memory cells. When only a limited number of blocks are repeatedly used, the device can prematurely wear out. By even distributing the program/erase cycles over the entire flash storage device, the ATP Enhanced Wear Leveling mechanism makes sure that all memory cells are used to the maximum, thereby extending the life span of the device.

For more information on ATP’s wear leveling techniques and other technologies that extend the life expectancy of its “Industrial Only” flash storage products, visit the ATP website or contact an ATP Representative.