NAND flash cells are arranged in pages and blocks. Data is written on pages, but the minimum unit of erasing is by blocks. Due to the nature of flash, the cells wear out with each program and erase (P/E) cycle, rendering the flash storage usable for a finite period of time.

In the past, the life expectancy of flash was largely dependent on its type. Single-level cell (SLC), which stores only one bit per cell, was deemed the most reliable and longest enduring. Multi-level cell (MLC), which stores two bits per cell, was rated next to SLC. Triple- and quad-level cell TLC/QLC were rated for consumer use only and were not considered fit for the demands of enterprise and industrial applications due to their low endurance.

Thanks to big strides in technology, flash storage has come a long way largely due to powerful flash controllers that enable greater reliability and longer usable product life.

In this article, we discuss one of the most common flash controller functions that help maximize the life expectancy of flash storage.

Wear Leveling

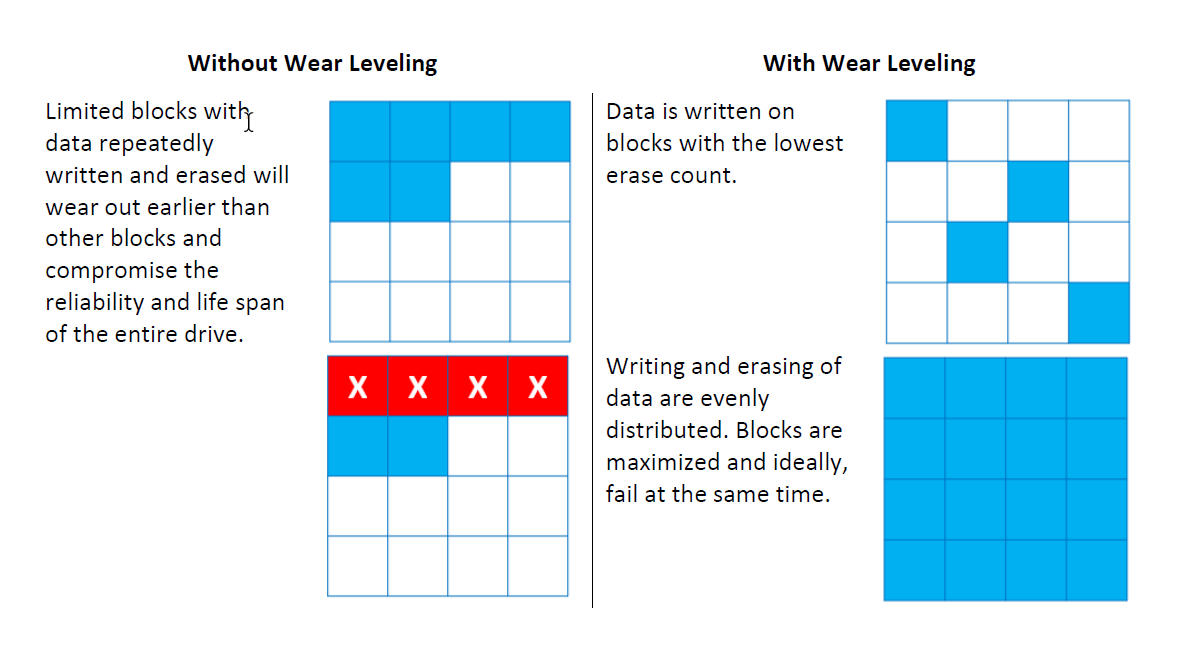

Wear leveling mechanisms allow the flash storage device to evenly distribute the P/E cycles among all blocks. It prevents the premature wearout of overused blocks, so all blocks can be used to the maximum. Wear leveling extends the life span and improves the reliability and durability of the storage device.

Figure 1. A graphical representation of a storage device with and without wear leveling.

There are three types of wear leveling.

- Dynamic. Makes sure that data is written only on blocks with the lowest erase count. The downside is that wear leveling is limited only to “hot” or frequently modified areas, so blocks that hold rarely accessed, static data are not included in the pool of free space, thus limiting the number of blocks going through wear leveling.

- Static – Includes static data or “cold” blocks in the wear leveling process. If a block contains static or rarely accessed data, its write/erase count is low. The data is moved from “cold” blocks to “hot” blocks and the freed-up block is added to the pool of free space for future use. Reassigning static data is a more complex process because it involves multiple operations to move static data around. While more effective at extending flash storage life span, static wear leveling only covers a single flash die.

- Global – Works like static wear leveling by including both free space and blocks with static data, but the main difference is that its coverage extends to the entire flash storage device.

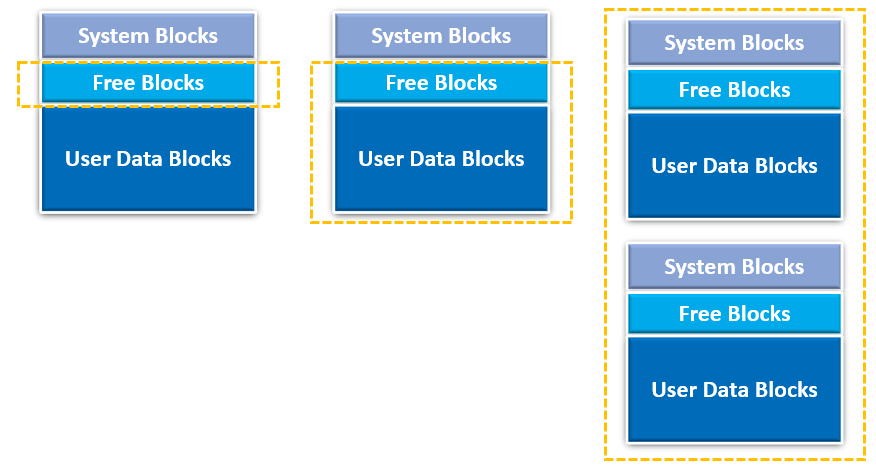

The following figure illustrates the differences in executed areas:

|

Dynamic Wear Leveling

|

Static Wear Leveling

|

Global Wear Leveling

|

Figure 2. Differences in executed areas for Dynamic, Static and Global Wear Leveling. Image Reference: Embedded Computing

ATP Enhanced Wear Leveling

ATP implements global wear leveling on its flash memory products, using an advanced algorithm that carries out both dynamic and static wear leveling to ensure that the flash product is used to the fullest extent of its life span.

ATP Enhanced Wear Leveling treats and manages all NAND flash components in ONE drive as a unified memory management unit. The wear leveling is carried out by the flash controller and is independent of the host system, thus minimizing impact on system performance.

How it works:

There are four main steps for the “enhanced wear leveling” mechanism:

- Establish and update the link table, which is used to convert the host’s logical address to the flash memory’s physical address.

- Record the “erase counts” of all the blocks in one zone and save them to the wear leveling table. The table is maintained by a RAM register unit in the controller. The table will keep every block’s “erase count” within the flash memory ICs.

- Find the static block (with “0” erase count) and save this block address in the wear leveling pointer. The pointer is used to select the next available block to be swapped.

- Check the “erase count” when a block is taken out from the spare pool. If an over-count block is bigger than the spare block, swap the static spare block with over-count block. “Over-count” means that the block’s erase count is already higher than the Wear Count Register, and this block should be swapped as soon as possible.

Conclusion

Wear leveling is needed to address the finite program/erase capability of NAND flash memory cells. When only a limited number of blocks are repeatedly used, the device can prematurely wear out. By even distributing the program/erase cycles over the entire flash storage device, the ATP Enhanced Wear Leveling mechanism makes sure that all memory cells are used to the maximum, thereby extending the life span of the device.

For more information on ATP’s wear leveling techniques and other technologies that extend the life expectancy of its “Industrial Only” flash storage products, visit the ATP website or contact an ATP Representative.